Режим ЕСР

Протокол ЕСР (Extended Capability Port — порт с расширенными возможностями) был предложен Hewlett Packard и Microsoft для связи с ПУ типа принтеров или сканеров. Как и ЕРР, данный протокол обеспечивает высокопроизводительный двунаправленный обмен данными хоста с ПУ. Протокол ЕСР в обоих направлениях обеспечивает два типа циклов:

¦ циклы записи и чтения данных;

¦ командные циклы записи и чтения.

Командные циклы подразделяются на два типа: передача канальных адресов и передача счетчика RLC (Run-Length Count).

30

Глава 1. Параллельный интерфейс — LPT-порт

В отличие от ЕРР вместе с протоколом ЕСР сразу появился стандарт на программную (регистровую) модель его адаптера, изложенный в документе «The IEEE 1284 Extended Capabilities Port Protocol and ISA Interface Standard» компании Microsoft. Этот документ определяет свойства протокола, не заданные стандартом IEEE 1284:

¦ компрессия данных хост-адаптером по методу RLE;

¦ буферизация FIFO для прямого и обратного каналов;

¦ применение DMA и программного ввода-вывода.

Компрессия в реальном времени по методу RLE (Run-Length Encoding) позволяет достичь коэффициента сжатия 64:1 при передаче растровых изображений, которые имеют длинные строки повторяющихся байт. Компрессию можно использовать, только если ее поддерживают и хост, и ПУ.

Канальная адресация ЕСР применяется для адресации множества логических устройств, входящих в одно физическое. Например, в комбинированном устройстве факс/принтер/модем, подключаемом только к одному параллельному порту, возможен одновременный прием факса и печать на принтере. В режиме SPP, если принтер установит сигнал занятости, канал будет занят данными, пока принтер их не примет. В режиме ЕСР программный драйвер просто адресуется к другому логическому каналу того же порта.

Протокол ЕСР переопределяет сигналы SPP (табл. 1.6). Таблица 1.6. Сигналы LPT-порта в режиме ввода-вывода ЕСР

|

||

|

|

Контакт Сигнал SPP Имя в ЕСР |

|

HostClk HostAck |

|

Strobe# AutoLF* |

|

1 14 |

О Указывает тип цикла (команда/данные) при передаче в прямом направлении. Используется как сигнал подтверждения в паре с PeriphClk для передачи в обратном направлении

|

17 |

Selectln* |

1284Active |

0 |

|

16 |

lnit# |

ReverseRequest# |

0 |

|

10 |

Ack# |

PeriphClk |

I |

|

11 |

Busy |

PeriphAck |

I |

|

12 |

PaperEnd |

AckReverse* |

I |

|

13 |

Select |

Xflag1 |

I |

в режиме IEEE 1284 (в режиме SPP уровень

низкий)

Запрос реверса. Низкий уровень сигнализирует о переключении канала на передачу в обратном направлении

Строб данных, используется в паре с HostAck для передачи в обратном направлении

Используется как сигнал подтверждения в паре с HostClk для передачи в прямом направлении. Индицирует тип команда/ данные при передаче в обратном направлении

Подтверждение реверса. Переводится

в низкий уровень в ответ на ReverseRequest*

Флаг расширяемости

1.3. Стандарт IEEE 1284

Контакт Сигнал SPP Имя в ЕСР I/O Описание

на доступность (наличие) обратного канала передачи1

2-9 Data [0:7] Data [0:7] I/O Двунаправленный канал данных

Адаптер ЕСР тоже генерирует внешние протокольные сигналы квитирования аппаратно, но его работа существенно отличается от режима ЕРР.

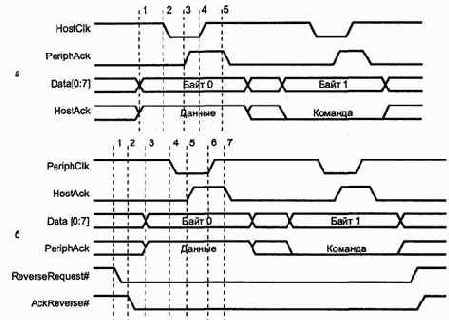

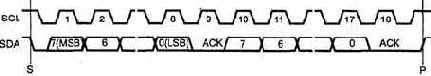

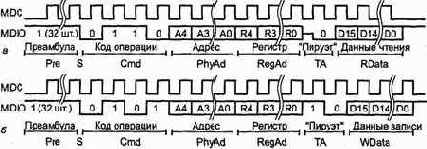

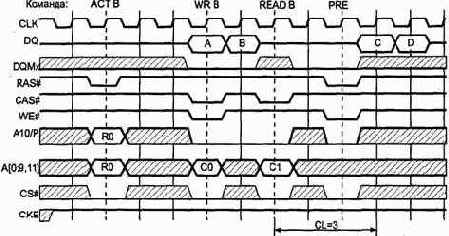

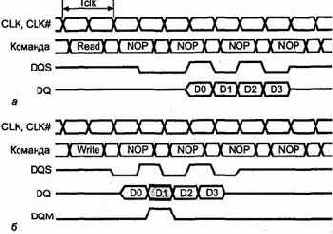

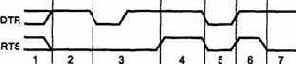

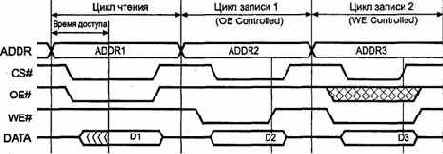

На рис. 1.5, а приведена диаграмма двух циклов прямой передачи: за циклом данных следует командный цикл. Тип цикла задается уровнем на линии HostAck: в цикле данных — высокий, в командном цикле — низкий. В командном цикле байт может содержать канальный адрес или счетчик RLE. Отличительным признаком является бит 7 (старший): если он нулевой, то биты 0-6 содержат счетчик RLE (0-127), если единичный — то канальный адрес.

На рис. 1.5, б показана пара циклов обратной передачи.

В отличие от диаграмм обмена ЕРР, на рис. 1.5 не приведены сигналы циклов системной шины процессора. В данном режиме обмен программы с ПУ разбивается на два относительно независимых процесса, которые связаны через FIFO-буфер. Обмен драйвера с FIFO-буфером может осуществляться как с использованием DMA, так и программного ввода-вывода. Обмен ПУ с буфером аппаратно выполняет адаптер ЕСР. Драйвер в режиме ЕСР не имеет информации о точном состоянии процесса обмена, но обычно важно только то, завершен он или нет.

Прямая передача данных на внешнем интерфейсе состоит из следующих шагов:

1. Хост помещает данные на шину канала и устанавливает признак цикла дан

ных (высокий уровень) или команды (низкий уровень) на линии HostAck.

2. Хост устанавливает низкий уровень на линии HostClk, указывая на действи

тельность данных.

3. ПУ отвечает установкой высокого уровня на линии PeriphAck.

4. Хост устанавливает высокий уровень линии HostClk, и этот перепад может использоваться для фиксации данных в ПУ.

5. ПУ устанавливает низкий уровень на линии PeriphAck для указания на готовность к приему следующего байта.

Поскольку передача в ЕСР происходит через FIFO-буферы, которые могут присутствовать на обеих сторонах интерфейса, важно понимать, на каком этапе данные можно считать переданными. Данные считаются переданными на шаге 4, когда линия HostClk переходит в высокий уровень. В этот момент модифицируются счетчики переданных и принятых байт. В протоколе ЕСР есть условия, вызывающие прекращение обмена между шагами 3 и 4. Тогда эти данные не должны рассматриваться как переданные.

32

Глава 1. Параллельный интерфейс — LPT-nopr

Рис. 1.5. Передача в режиме ЕСР: а — прямая, б — обратная

Из рис. 1.5 видно и другое отличие ЕСР от ЕРР. Протокол ЕРР позволяет драйверу чередовать циклы прямой и обратной передачи, не запрашивая подтверждения на смену направления.

В ЕСР смена направления должна быть согласована: хост запрашивает реверс установкой ReverseRequest*, после чего он должен дождаться подтверждения сигналом AckReverse*. Поскольку предыдущий цикл мог выполняться по прямому доступу, драйвер должен дождаться завершения прямого доступа или прервать его, выгрузить буфер FIFO, определив точное значение счетчика переданных байт, и только после этого запрашивать реверс.

Обратная передача данных состоит из следующих шагов:

1. Хост запрашивает изменение направления канала, устанавливая низкий уро

вень на линии ReverseRequest*.

2. ПУ разрешает смену направления установкой низкого уровня на линии

AckReverse*.

3. ПУ помещает данные на шину канала и устанавливает признак цикла данных

(высокий уровень) или команды (низкий уровень) на линии PeriphAck.

4. ПУ устанавливает низкий уровень на линии PeriphClk, указывая на действи

тельность данных.

5. Хост отвечает установкой высокого уровня на линии HostAck.

1.3. Стандарт IEEE 1284_______________________________________________ 33

6. ПУ устанавливает высокий уровень линии PeriphClk; этот перепад может использоваться для фиксации данных хостом.

7. Хост устанавливает низкий уровень на линии HostAck для указания на готовность к приему следующего байта.

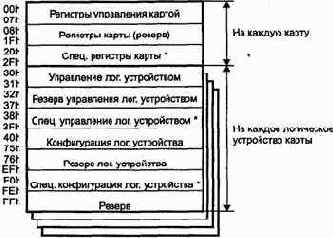

Режимы и регистры ЕСР-порта

Программный интерфейс и регистры ЕСР для адаптеров IEEE 1284 определяет спецификация Microsoft. Порт ЕСР может работать в различных режимах, приведенных в табл. 1.7, где код соответствует полю Mode регистра ECR (биты [7:5]).

Таблица 1.7. Режимы ЕСР-порта

0

1 Bi-directional mode, двунаправленный порт (тип 1 для PS/2)

10 Fast Centronics, однонаправленный с использованием FIFO и DMA

11 ЕСР Parallel Port mode, собственно режим ЕСР

100 ЕРР Parallel Port mode, режим ЕРР1

101 Зарезервировано

110 Test mode, тестирование работы FIFO и прерываний

111 Configuration mode, доступ к конфигурационным регистрам

Регистровая модель адаптера ЕСР (табл. 1.8) использует свойства архитектуры стандартной шины и адаптеров ISA, где для дешифрации адресов портов ввода-вывода задействуются только 10 младших линий шины адреса. Поэтому, например, обращения по адресам Port, Port+400h, Port+800h... будут восприниматься как обращения к адресу Port, лежащему в диапазоне 0-3FFh. Современные PC и адаптеры декодируют большее количество адресных бит, поэтому обращения по адресам 0378h и 0778Н будут адресованы двум различным регистрам. Помещение дополнительных регистров ЕСР «за спину» регистров стандартного порта (смещение 400-402Н) преследует две цели. Во-первых, эти адреса никогда не использовались традиционными адаптерами и их драйверами, и их применение в ЕСР не приведет к сужению доступного адресного пространства ввода-вывода. Во-вторых, этим обеспечивается совместимость со старыми адаптерами на уровне режимов 000-001 и возможность определения факта присутствия ЕСР-адаптера посредством обращения к его расширенным регистрам.

Каждому режиму ЕСР соответствуют (и доступны) свои функциональные регистры. Переключение режимов осуществляется записью в регистр ECR. «Дежурными» режимами, включаемыми по умолчанию, являются 000 или 001. В любом из них работает полубайтный режим ввода. Из этих режимов всегда можно переключиться в любой другой, но из старших режимов (010-111) переключение возмож-

34_____________________________ Глава 1. Параллельный интерфейд — LPT-порт

но только в 000 или 001. Для корректной работы интерфейса перед выходом из старших режимов необходимо дождаться завершения обмена по прямому доступу и очистки FIFO-буфера.

В режиме 000 (SPP) порт работает как однонаправленный программно-управляемый SPP-порт.

В режиме 001 (Bi-Di PS/2) порт работает как двунаправленный порт PS/2 типа 1. От режима 000 отличается возможностью реверса канала данных по биту CR. 5.

Режим 010 (Fast Centronics) предназначен только для высокопроизводительного вывода через FIFO-буфер с использованием DMA. Сигналы квитирования по протоколу Centronics вырабатываются аппаратно. Сигнал запроса прерывания вырабатывается по состоянию FIFO-буфера, но не по сигналу Ack# (запрос одиночного байта «не интересует» драйвер быстрого блочного вывода).

Режим 011 является собственно режимом ЕСР, описанным выше, Поток данных и команд, передаваемых в ПУ, помещается в FIFO-буфер через регистры ECPDFIFO и ECPAFIFO соответственно. Из FIFO они выводятся с соответствующим признаком цикла (состояние линии HostAck). Принимаемый поток данных от ПУ извлекается из FIFO-буфера через регистр ECPDFIFO. Получение адреса в командном цикле от ПУ не предусматривается. Обмен с регистром ECPDFIFO может производиться и по каналу DMA.

Компрессия по методу RLE при передаче выполняется программно. Для передачи подряд более двух одинаковых байт данных в регистр ЕС PAFIFO записывается байт, у которого младшие 7 бит содержат счетчик RLC (значение RLC-127 соответствует 128 повторам), а старший бит нулевой..После этого в ECPDFIFO записывается сам байт.

Принимая эту пару байт (командный байт и байт данных), ПУ осуще ствляет декомпрессию. При приеме потока от ПУ адаптер ЕСР декомпрессию осуществляет аппаратно и в FIFO-буфер помещает уже декомпрессированные данные. Отсюда очевидно, что вывод данных с одновременным использованием компрессии и DMA невозможен.

Режим 100 (ЕРР) — один из способов включения режима ЕРР (если таковой поддерживается адаптером и разрешен в CMOS Setup).

Режим 110 (Test Mode) предназначен для тестирования взаимодействия FIFO и прерываний. Данные могут передаваться в регистр TFIFO и из него с помощью DMA или программным способом. На внешний интерфейс обмен не воздействует. Адаптер отрабатывает операции вхолостую на максимальной скорости интерфейса (как будто сигналы квитирования приходят без задержек). Адаптер следит за состоянием буфера и по мере необходимости вырабатывает сигналы запроса прерывания. Таким образом программа может определить максимальную пропускную способность канала.

Режим 111 (Configuration mode) предназначен для доступа к конфигурационным регистрам. Выделение режима защищает адаптер и протокол от некорректных изменений конфигурации в процессе обмена.

Как уже упоминалось, каждому режиму ЕСР соответствуют свои функциональные регистры (табл. 1.8).

|

35 |

|

Таблица 1.8. |

Регистры ЕСР |

|||

|

Смещение |

Имя |

R/W |

Режимы ЕСР1 |

Название |

|

000 |

DR |

R/W |

000-001 |

Data Register |

|

000 |

ECPAFIFO |

R/W |

011 |

ЕСР Address FIFO |

|

001 |

SR |

R/W |

Все |

Status Register |

|

002 |

CR |

R/W |

Все |

Control Register |

|

400 |

SDFIFO |

R/W |

010 |

Parallel Port Data FIFO |

|

400 |

ECPDFIFO |

R/W |

011 |

ECP Data FIFO |

|

400 |

TFIFO |

R/W |

110 |

Test FIFO |

|

400 |

ECPCFGA |

R |

111 |

Configuration Register A |

|

401 |

ECPCFGB |

R/W |

111 |

Configuration Register В |

|

402 |

ECR |

R/W |

Все |

Extended Control Register |

Регистр данных DR используется для передачи данных только в программно-управляемых режимах (000 и 001).

Регистр состояния SR передает значение сигналов на соответствующих линиях (как в SPP).

Регистр управления CR имеет назначение бит, совпадающее с SPP. В режимах 010,011 запись в биты 0,1 (сигналы AutoLF* и Strobe*) игнорируется. Регистр ECPAFIFO служит для помещения информации командных циклов (канального адреса или счетчика RLE, в зависимости от бита?) в FIFO-буфер. Из буфера информация будет выдана в командном цикле вывода. Регистр SDFIFO используется для передачи данных в режиме010. Данные, записанные в регистр (или посланные по каналу DMA), передаются через буфер FIFO по реализованному аппаратно протоколу Centronics. При этом должно быть задано прямое направление передачи (бит CR. 5-0).

Регистр DFIFO используется для обмена данными в режиме 011 (ЕСР). Данные, записанные в регистр или считанные из него (или переданные по каналу DMA), передаются через буфер FIFO по протоколу ЕСР.

Регистр TFIFO обеспечивает механизм тестирования FIFO-буфера в режиме 110.

Регистр ECPCFGA позволяет считывать информацию об адаптере (идентификационный код в битах [7:4]).

Регистр ECPCFGB позволят хранить любую информацию, необходимую драйверу. Запись в регистр не влияет на работу порта.

Регистр ECR — главный управляющий регистр ЕСР. Его биты имеют следующее назначение:

¦ ECR[7:5] -ЕСР MODE - задают режим ЕСР;

¦ ECR. 4 — ERRINTREN* — (Error Interrupt Disable) запрещает прерывания по сигналу Error* (при нулевом значении бита по отрицательному перепаду на этой линии вырабатывается запрос прерывания);

36_____________________________ Глава 1. Параллельный интерфейс— LPT-порт

¦ ECR. 3 — DMAEN — (DMA Enable) разрешает обмен по каналу DMA;

¦ ECR. 2 — SERVICEINTR — (Service Interrupt) запрещает сервисные прерывания, которые вырабатываются по окончании цикла DMA (если он разрешен), по порогу заполнения/опустошения FIFO-буфера (если не используется DMA) и по ошибке переполнения буфера сверху или снизу;

¦ ECR.1 — FIFOFS — (FIFO Full Status) сигнализирует о заполнении буфера; при FIFOFS= lb буфере нет ни одного свободного байта;

¦ ECR.0 — FIFOES — (FIFO Empty Status) указывает на полное опустошение буфера; комбинация FIFOFS=FIFOES=1 означает ошибку работы с FIFO (переполнение сверху или снизу).

Когда порт находится в стандартном или двунаправленном режимах (000 или 001), первые три регистра полностью совпадают с регистрами стандартного порта. Так обеспечивается совместимость драйвера со старыми адаптерами и старых драйверов с новыми адаптерами.

По интерфейсу с программой ЕСР-порт напоминает ЕРР: после установки режима (записи кода в регистр ECR) обмен данными с устройством сводится к чтению или записи в соответствующие регистры. За состоянием FIFO-буфера наблюдают либо по регистру ECR, либо по обслуживанию сервисных прерываний от порта. Весь протокол квитирования генерируется адаптером аппаратно. Обмен данными с ЕСР-портом (кроме явного программного) возможен и по прямому доступу к памяти (каналу DMA), что эффективно при передаче больших блоков данных.

Родственные интерфейсы и преобразователи уровней

В последовательном интерфейсе далеко не всегда используют двуполярные сигналы RS-232C — это неудобно, хотя бы из-за необходимости использования дву-полярного питания приемопередатчиков. Сами микросхемы вышеописанных приемопередатчиков UART работают с сигналами логики ТТЛ или КМОП; такие же сигналы используются, например, и в сервисных портах винчестеров и других устройств. Многие устройства (в том числе карманные ПК и мобильные телефоны) имеют внешний последовательный интерфейс с уровнями низковольтной логики. Конечно, сигналы обычной логики не имеют столь высокой помехоустойчивости, как RS-232C, но не всегда это и требуется.

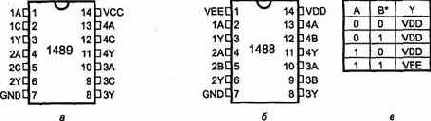

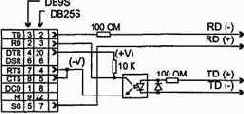

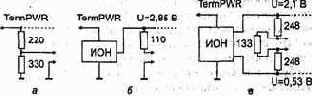

Для взаимного преобразования уровней интерфейса RS-232C и логики специально выпускаются буферные микросхемы приемников (с гистерезисом) и передатчиков двуполярного сигнала. При несоблюдении правил заземления и коммутации они обычно становятся первыми жертвами «пиротехнических» эффектов. Раньше их нередко устанавливали в «кроватки», что облегчало их замену. Цоко-левка популярных микросхем формирователей сигналов RS-232C приведена на рис. 2.7. Часто буферные схемы входят прямо в состав интерфейсных БИС. Это удешевляет изделие, экономит место на плате, но в случае аварии оборачивается крупными финансовыми потерями. Вывести из строя интерфейсные микросхемы замыканием сигнальных цепей маловероятно: ток короткого замыкания передатчиков обычно не превышает 20 мА.

В специальных кабелях-адаптерах часто применяют преобразователи уровней фирмы Maxim и Sypex; они удобны тем, что содержат и приемники, и передатчики. Из широкого ассортимента этих преобразователей легко подобрать подходящий по количеству приемников и передатчиков, а также по питанию (однополяр-ному, двуполярному, низковольтному).

2.2. Родственные интерфейсы и преобразователи уровней 55

|

Рис. 2.7. Формирователи сигналов RS-232C: а — приемник 1489 (А — вход RS-232,

С ^ управление гистерезисом (ТТЛ), Y — выход ТТЛ); б — передатчик 1488

(А, В — входы ТТЛ, Y — выход RS-232, VDD = +12 В, VEE = -12 В); в — таблица

состояния выходов передатчика (*1 В — логическая единица)

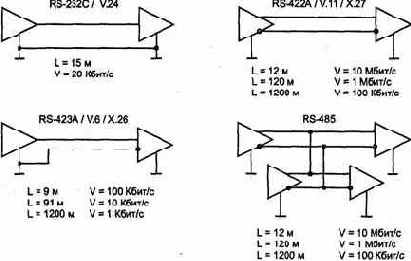

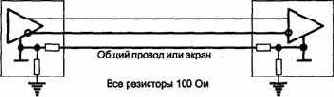

Когда требуется большая помехоустойчивость (дальность и скорость передачи), применяют иные электрические варианты последовательных интерфейсов: RS-422A (V.11, Х.27), RS-423A (V.10, Х.26), RS-485. На рис. 2.8 приведены схемы соединения приемников и передатчиков, а также показаны ограничения на длину линии (L) и максимальную скорость передачи данных (V). Несимметричные линии интерфейсов RS-232C и RS-423A имеют самую низкую защищенность от синфазной помехи, хотя дифференциальный вход приемника RS-423A позволяет в какой-то мере исправить ситуацию. Лучшие параметры имеют интерфейсы RS-422A и RS-485, работающие на симметричных линиях связи. В них для передачи каждого сигнала используются дифференциальные приемопередатчики с отдельной (витой) парой проводов для каждой сигнальной цепи.

|

Рис. 2.8. Стандарты последовательных интерфейсов

56

Глава 2. Последовательный интерфейс — СОМ-порт

Интерфейсы EIA-RS-422 (ITU-T V.ll, X.27) и EIA-RS-485 (ISO 8482) используют симметричную передачу сигнала и допускают как двухточечную, так и шинную топологию соединений. В них информативной является разность потенциалов между проводниками А и В. Если на входе приемника UA-UB>0,2 В (А положи-тельнее В) — состояние «выключено» (space), UA-UB<-0,2 В (А отрицательнее В) — состояние «включено» (mark). Диапазон |UA-UB|<0,2 В является зоной нечувствительности (гистерезис), защищающей от воздействия помех. На выходах передатчика сигналы UA и UB обычно переключаются между уровнями 0 и +5 В (КМОП) или +1 и +4 В (ТТЛ), дифференциальное выходное напряжение должно лежать в диапазоне 1,5-5 В. Выходное сопротивление передатчиков 100 Ом. Интерфейсы электрически совместимы между собой, хотя и имеют некоторые различия в ограничениях. Принципиальное отличие передатчиков RS-485 — возможность переключения в третье состояние.

Передатчики RS-422/485 совместимы с приемниками RS-423. Основные параметры интерфейсов приведены в табл. 2.3, топологию соединений иллюстрирует рис. 2.9.

Чтобы увеличить число узлов, можно повысить входное сопротивление приемников, но при этом снижается допустимая скорость или максимально возможная дальность передачи. Максимальная скорость передачи на коротких расстояниях (до 10 м) ограничивается быстродействием передатчиков (достижима частота 25 МГц). На средних расстояниях ограничение определяется емкостью кабеля (1200 бит/с - 25 нФ, 9600 бит/с - 30 нФ, 115 кбит/с -250 пФ). Максимальная дальность (1200 м) ограничена сопротивлением петли постоянному току.

Таблица 2.3. Параметры интерфейсов RS-422 и RS-485

Параметр____________________________________ RS-422____________ RS-485_____________

|

0,2 |

0,2 |

|

-6,8...+6,8 |

-6,8...+11,8 |

|

-7...+7 |

-7...+12 |

|

4 |

12 |

|

10060 |

60 |

|

1 передатчик |

32 (передатчиков, |

|

+10 приемников |

приемников или |

|

их комбинаций) |

|

|

1200 (100 кбит/с) |

1200 (100 кбит/с) |

|

12(10Мбит/с) |

12(10Мбит/с) |

|

На дальнем конце |

На обоих концах |

|

от передатчика |

|

|

<150Ha шинуGND |

<250 на шину |

|

с потенциалом |

|

|

-7...+12 Вили между |

|

|

проводами А и В |

Минимальное сопротивление нагрузки передатчика, Ом

Максимальное число узлов

Максимальная длина, м Терминаторы, R=100Ом Ток короткого замыкания, мА

2.2. Родственные интерфейсы и преобразователи уровней

57

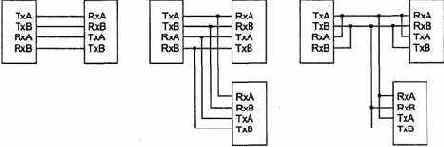

А б в

Рис. 2.9. Топология интерфейсов: а — RS-422, б — RS-485 четырехпроводный, в — RS-485 двухпроводный

Интерфейс RS-485 может быть в двух версиях: двухпроводной и четырехпровод-ной.

Четырехпроводная версия (рис. 2.9, б) выделяет задающий узел (master), передатчик которого работает на приемники всех остальных. Передатчик задающего узла всегда активен — переход в третье состояние ему не нужен. Передатчики остальных ведомых (slave) узлов должны иметь тристабильные выходы, они объединяются на общей шине с приемником ведущего узла. В двухпроводной версии (рис. 2.9, в) все узлы равноправны.

В вырожденном случае — при двухточечном соединении — интерфейсы RS-485 и RS-422 эквивалентны, и третье состояние не используется.

Для определенности состояния покоя шины RS-485, когда нет активных передатчиков, на линию устанавливают активные терминаторы, «растягивающие» потенциалы проводов. В покое провод В должен иметь более положительный потенциал, чем А.

При многоточечном соединении необходимо организовать метод доступа к среде передачи. Чаще всего используют полинг (polling) — опрос готовности к передаче, выполняемый ведущим устройством, или передачу права доступа в соответствии с определенным (установленным) регламентом. Иногда используют и методы случайного доступа (аналогично Ethernet).

Дифференциальный вход интерфейсов защищает от действия помех, но при этом должно осуществляться соединение «схемных земель» устройств между собой и с шиной заземления. Для соединения устройств между собой используют третий провод интерфейса (можно и экран). Для того чтобы по третьему проводу не протекал большой ток, выравнивающий «земляные потенциалы», в его цепь включают резисторы (рис. 2.10).

Интерфейс RS-422 часто используется для подключения периферийных устройств (например, принтеров). Интерфейс RS-485 популярен в качестве шин устройств промышленной автоматики.

Интерфейс «токовая петля» для представления сигнала использует не напряжение, а ток в двухпроводной линии, соединяющей приемник и передатчик.

58

Глава 2. Последовательный интерфейс — СОМ-порт

Логической единице (состоянию «включено») соответствует протекание тока 20 мА, а логическому нулю — отсутствие тока.

Такое представление сигналов для вышеописанного формата асинхронной посылки позволяет обнаружить обрыв линии — приемник заметит отсутствие стоп-бита (обрыв линии действует как постоянный логический нуль).

Рис. 2.10. Соединение «схемных земель» для интерфейсов RS-422 и RS-485

Токовая петля обычно предполагает гальваническую развязку входных цепей приемника от схемы устройства. При этом источником тока в петле является передатчик (этот вариант называют активным передатчиком). Возможно и питание от приемника (активный приемник), при этом выходной ключ передатчика может быть также гальванически развязан с остальной схемой передатчика. Существуют упрощенные варианты без гальванической развязки, но это уже вырожденный случай интерфейса. Заметим, что интерфейс MIDI (см. п. 8.5.3) с «классической» токовой петлей несовместим.

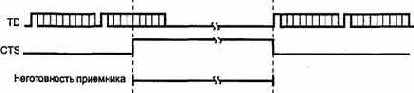

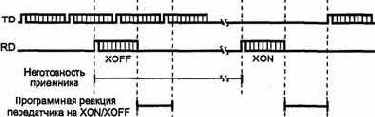

Токовая петля с гальванической развязкой позволяет передавать сигналы на расстояния до нескольких километров, но при невысоких скоростях (выше 19 200 бит/с не используют, а на километровых расстояниях допустима скорость до 9600 бит/с и ниже). Допустимое расстояние определяется сопротивлением пары проводов и уровнем помех. Поскольку интерфейс требует пары проводов для каждого сигнала, обычно используют только два сигнала последовательного интерфейса (4-проводная линия). В случае двунаправленного обмена применяются только сигналы передаваемых и принимаемых данных, а для управления потоком используется программный метод XON/XOFF. Если двунаправленный обмен не требуется, применяют одну линию данных, а для управления потоком обратная линия задействуется для сигнала CTS (аппаратный протокол) или встречной линии данных (программный протокол). При надлежащем ПО одной токовой петлей можно обеспечить двунаправленную полудуплексную связь двух устройств. При этом каждый приемник «слышит» как сигналы передатчика на противоположной стороне канала, так и сигналы своего передатчика. Они расцениваются коммуникационными пакетами просто как эхо-сигнал.

Для безошибочного приема передатчики должны работать поочередно.

Токовая петля позволяет использовать выделенные физические линии без модемов, но на малых скоростях. Иногда по токовой петле подключают терминалы с интерфейсом RS-232C, если не хватает штатной длины интерфейса или требуется гальваническая развязка. Преобразовать сигналы RS-232C в токовую петлю несложно — на рис. 2.11 приведена простейшая схема преобразователя примени-

2.3. Асинхронный режим передачи

59

тельно к подключению терминала. Для получения двуполярного сигнала, требуемого для входных сигналов СОМ-порта, применяется питание от интерфейса. Схема может быть усложнена для защиты оптронов от перегрузки и улучшения формы потенциальных сигналов. Допустимая скорость определяется и быстродействием применяемых оптронов (скорость 9600 бит/с достигается практически на любых оптронах).

Рис. 2.11. Преобразование интерфейса RS-232C в «токовую петлю»

ROM BIOS карт ISA PnP

Для поддержки технологии PnP и расширения возможностей управления начальной загрузкой в спецификации PnP BIOS ввели дополнительный указатель на структуру расширенного заголовка (Expansion Header Structure). Расширенный заголовок имеет формат, приведенный в табл. 12.9. В одном ПЗУ может находиться несколько расширенных заголовков (это требуется для многофункциональных карт расширения), связанных в цепочку. В каждом расширенном заголовке может указываться смещение следующего заголовка относительно начала стандартного заголовка. Наличие и действительность расширенного заголовка проверяется по его сигнатуре и контрольной сумме. Сумма всех байтов расширенного заголовка, включая байт контрольной суммы, должна быть нулевой.

Таблица 12.9. Расширенный заголовок ROM BIOS карт ISA PnP

| Смещение | Длина | Назначение | |||

| Oh | 4 байта | Сигнатура, строка $PnP (символы ASCII) | |||

| 04h | байт | Версия структуры (01 h) | |||

| 05h | байт | Длина (в параграфах по 16 байт) | |||

| 06h | слово | Смещение следующего заголовка (OOOOh, если нет больше) | |||

| 08h | байт | Резерв(0) | |||

| 09h | байт | Контрольная сумма | |||

| OAh | двойное слово | Идентификатор устройства PnP | |||

| OEh | слово | Указатель на строку идентификатора производителя (0, если нет) | |||

| 10h | слово | Указатель на строку названия продукта (0, если нет) | |||

| 12h | Збайт | Код типа устройства |

12.9. Расширения ROM BIOS__________________________________________ 501

Смещение Длина Назначение

| 15h | байт | ||

| 16h | слови | ||

| 18h | слово | ||

| 1Ah | слово | ||

| 1Ch | слово | ||

| 1Eh | слово |

Вектор подключения BCV (Boot Connection Vector) — 0, если нет

Вектор отключения (Disconnect Vector) — 0, если нет

Точка входа для загрузки BEV (Bootstrap Entry Point) — 0, если нет

Резерв (0)

Вектор получения информации о статических ресурсах (Static Resource Information Vector) — Real/Protected mode (0 если нет)

Код типа состоит из байта общего типа, байта подтипа и байта идентификатора программного интерфейса, по которым система может узнать знакомые устройства.

Байт индикаторов устройства имеет следующее назначение битов:

¦ бит 7 — ПЗУ поддерживает модель инициализации устройства (Device Driver Initialization Model);

¦ бит 6 — ПЗУ может затеняться оперативной памятью;

¦ бит 5 — ПЗУ может каптироваться по чтению;

¦ бит 4 — ПЗУ требуется лишь для загрузки с данного устройства;

¦ бит 3 — резерв (0);

¦ бит 2 — является устройством загрузки (IPL-устройство);

¦ бит 1 — устройство ввода (может заменять клавиатуру);

¦ бит 0 — устройство вывода (дисплей).

Вектор подключения BCV (Boot Connection Vector, он же Interrupt Connection Vector) указывает смещение для процедуры, дальний вызов которой приведет к перехвату векторов прерываний первичных устройств ввода, вывода или загрузки (сервисов Int 9h, Int 10п или Int 13h соответственно), в зависимости от параметров, переданных в регистрах процессора. При вызове этой процедуры в регистре АХ единицы в битах 0,1 и 2 запрашивают перехват сервисов Int 9h, Int 10hилиInt 13п соответственно (остальные биты нулевые), ES: DI указывает на контрольную структуру PnP BIOS (System BIOS PnP Installation Check Structure), BX содержит селективный номер (CSN) карты ISA PnP (для других карт FFFFh); DX содержит адрес порта чтения ISA PnP (для других карт FFFFh).

Вектор отключения указывает на процедуру, восстанавливающую старое значение векторов при безуспешной попытке загрузки с данного устройства.

Точка входа для загрузки BEV требуется, если устройство может использоваться в качестве загрузочного, но не обеспечивает блочных функций сервиса Int 13h. Тогда системная микросхема BIOS может дальним вызовом вызвать эту процедуру вместо выполнения сервиса Int 19h.

Таким образом, например, может выполняться удаленная загрузка ( Remote Programm Loading, RPL) по сети.

502______ Глава 12. Архитектурные компоненты IBM PC-совместимого компьютера

Вектор получения информации о статических ресурсах задает смещение процедуры, вызов которой выгрузит в память дескрипторы занимаемых ресурсов (в форматах, аналогичных структурам для ISA PnP). Адрес буфера размером не менее 1024 байт задается регистрами ES: DI при вызове данной процедуры.

Процедура инициализации, которая начинается со смещения 3 в заголовке ПЗУ, для карт PnP должна подчиняться определенным требованиям (до этой спецификации специальных требований не было), принимать параметры и сообщать код возврата.

¦ При вызове процедуры Е S: DI указывает на контрольную структуру PnP BIOS, ВХ содержит CSN карты ISA PnP (для других карт FFFFh); DX — адрес порта чтения ISA PnP (для других карт FFFFh).

¦ При исполнении процедура может переопределять любые векторы прерыва

ний и изменять данные в BDA и Е BDA, но перед возвратом она обязана восстановить прежние указатели для Int 9h, Int 10h, Int 13h и все прежние значения связанных с ними переменных в BDA и EBDA.

¦ При возврате в АХ возвращаются признаки проинициализированного устройства:

• бит 8 — устройство начальной загрузки, поддерживающее блочные функции INT 13h;

• бит 7 — устройство вывода, поддерживающее символьный вывод («телетайпный» режим) INT 10h;

• бит 6 — устройство ввода, поддерживающее символьный ввод I NT 9h;

• биты 5:4 — состояние подключения загрузочного устройства: 00 — не подключено, 01 — неизвестно, 10 — подключено (для устройства RPL соединение установлено), 11 — резерв;

• биты 3:2 — состояние подключения устройства вывода (аналогично предыдущему);

• биты 1:0 — состояние подключения устройства ввода (аналогично предыдущему).

Как видно из данного описания, расширенный заголовок и правила поведения процедуры инициализации позволяют системной BIOS более гибко пользоваться функциями дополнительных модулей BIOS — традиционные дополнительные модули со стороны системной BIOS были практически неуправляемыми. Заголовок данного вида может использоваться и картами ISA без поддержки PnP. Если эти карты будут передавать информацию о своих статических ресурсах, они окажут большую услугу для распределения ресурсов системой BIOS с поддержкой PnP. Таким образом, приспособить карту для работы в среде PnP можно всего лишь модификацией содержимого ее ПЗУ расширения BIOS.

Карта ISA PnP может быть установлена в разные системы, имеющие BIOS как с поддержкой PnP, так и без. Процедура инициализации должна исполняться адекватно обнаруженной среде: без PnP BIOS она должна работать традиционным способом, при необходимости загрузки перехватывая INT 19h, а в среде PnP BIOS она должна вести себя скромнее, лишь предоставляя системной BIOS требуемые интерфейсы и точки входа.

12.9. Расширения ROM BIOS__________________________________________ 503

Сервисы и прерывания BIOS

Системная BIOS предоставляет ряд сервисов низкого уровня, в основном предназначенных для обслуживания ввода-вывода и имеющих отношения к стандартным аппаратным интерфейсам. Традиционные сервисы BIOS обычно вызываются в реальном режиме или V86 посредством инструкций программных прерываний (Int xx). Большинство сервисов может быть вызвано и через фактически стандартизованные точки входа (адреса в области ROM BIOS) дальними вызовами процедур (CAL L f a r) с предварительным помещением в стек регистра флагов (сервисы построены как обработчики прерыаний). Все традиционные сервисы BIOS работают в 16-разрядном режиме процессора, и ими можно пользоваться в реальном режиме, V86 и малопривлекательном 16-разрядном защищенном режиме.

Для процессоров 386+ оптимальным по эффективности является 32-разрядный защищенный режим. Для того чтобы из этого режима можно было пользоваться сервисами BIOS (правда, не всеми) без промежуточных переключений, по инициативе фирмы Phoenix ввели 32-разрядные вызовы BIOS32. Адрес точки входа BIOS32 заранее не известен, но известен способ его нахождения: в диапазоне адресов памяти OEOOOO-OFFFFFh на границе параграфов (младшие 4 бита адреса нулевые) ищется строка-сигнатура "_32_" (число 325F5F33H) заголовка, за которой следует физический адрес точки входа. Сами сервисы вызываются дальними вызовами точки входа в сервис. Номер, параметры вызываемых функций и результаты передаются на регистрах процессора.

Прерывания, обслуживаемые системной BIOS, перечислены ниже. Кроме них несколько векторов используются как указатели на различные структуры данных.

12.8. Сервисы и прерывания BIOS____________________________________ 481

Внутренние прерывания:

¦ Int 00h — деление на 0;

¦ Int 01h — пошаговый режим;

¦ Int 03h — точка останова;

¦ Int 04h — переполнение;

¦ Int 06h — недопустимая команда 286+;

¦ Int 07h — вызов отсутствующего NPU.

Аппаратные прерывания:

¦ Int 02h — немаскируемое прерывание;

¦ Int 08h - таймер 8253/8254;

¦ Int 09h — клавиатура;

¦ Int 0Ah - IRQ2/9;

¦ Int 0Bh- IRQ3;

¦ Int 0Ch-IRQ4;

¦ Int 0Dh — IRQ5;

¦ Int 0Eh — IRQ6 — контроллер гибких дисков;

¦ Int 0Fh-IRQ7;

¦ Int 70h - CMOS-таймер;

¦ Int 7Ih — IRQ9 (перенаправлено на Int 0Ah);

¦ Int 72h- IRQ10;

¦ Int 73h — IRQ11;

¦ Int 74h — IRQ 12 (контроллер мыши PS/2);

¦ Int 75h — IRQ 13 — исключение сопроцессора;

¦ Int 76h — IRQ14— контроллер жестких дисков;

¦ Int 77h-IRQ15.

ПРИМЕЧАНИЕ

Прерывания Int 70h-77h имеют место только в AT.

¦ Int 05h (FOOO:FF54h) - печать экрана;

¦ Int 10h — видеосервис;

¦ Int llh — чтение списка оборудования (слово из BDA 0040:001 0h), возвра

щает в АХ:

• биты 15:14 — число обнаруженных LPT-портов: 00 —0,... 11 — 3;

• бит 13 — резерв;

• бит 12 — обнаружен игровой адаптер;

482______ Глава 12. Архитектурные компоненты IBM PC-совместимого компьютера

• биты 11:9 — число обнаруженных СОМ-портов: 000 —0,... 111 — 7;

• бит 8 — наличие контроллера DMA;

• биты 7:6 — число обнаруженных НГМД: 00 — 1,... 11 — 4;

• биты 5:4 — активный видеорежим: 00 — резерв, 10 — 80-колоночный цветной, 01 — 40-колоночный цветной, 11 — монохромный;

• биты 3:2 — размер ОЗУ на системной плате (теперь обычно 00);

• бит 1 — присутствие математического сопроцессора;

• бит 0 — присутствие дисководов;

¦ Int 12h — размер непрерывной памяти;

¦ Int 13h — дисковый сервис (блочный ввод-вывод);

¦ Int 14h — обслуживание СОМ-портов;

¦ Int 15h — АТ-функции (системный сервис, функции определяются значени

ем АН/АХ):

• 00-ОЗЬ — управление и обмен данными с кассетным магнитофоном (были когда-то и такие «стриммеры»!) на старых PC;

• 4fh — перехват клавиатуры;

• 53xxh — сервисы управления потреблением АРМ (Advanced Power Management);

• 8300h — запуск таймера, устанавливающего флаг в заданной ячейке;

• 830 lh — сброс того же таймера;

• 84h — джойстик (см. п. 8.6);

• 86h — программируемая задержка;

• 87h — перемещение блока расширенной памяти;

• 88h — получение размера расширенной памяти;

• 89h — переключение в режим V86;

• COh — получение системной конфигурации, при успешном выполнении (CF=0, AH=0) ES:BX указывает на таблицу данных конфигурации;

• 80-82h, 85h, 90h, 91h — функции многозадачных ОС (BIOS устанавливает

заглушки);

¦ Int 16h — клавиатурный ввод-вывод;

¦ Int 17h — обслуживание LPT-портов;

¦ Int 18h — процедура восстановления при неудаче начальной загрузки (прежде - ROM-Basic);

¦ Int 19h — начальная загрузка (вызов процедуры Bootstrap);

¦ Int lAh— системное время, дата, будильник и 16-битные вызовы сервисов PCI;

¦ Int IBh — обработчик нажатия клавиш Ctrl+Break;

12.8. Сервисы и прерывания BIOS____________________________________ 483

¦ Int I C h — User Timer Interrupt, процедура, вызываемая обработчиком I n t 0 8 h каждые 55 мс; BIOS устанавливает простую заглушку (IRET), но программы могут перехватывать это прерывание; на время отработки этой процедуры все аппаратные прерывания запрещены (кроме NMI).

¦ Int ЗЗп — поддержка мыши;

¦ Int 4Ah — обработчик будильника пользователя, установленного функцией

BIOS Int lAh(6); прерывание вызывается асинхронно, так что при возврате

из процедуры все регистры и флаги должны быть в том же состоянии, что и при

входе; BIOS ставит заглушку (IRET);

¦ Int 67h - EMS-функции.

Указатели на таблицы:

¦ Int IDh — видеопараметры;

¦ Int lEh — параметры дискет;

¦ Int IFh — знакогенератор СGA;

¦ Int 41h — параметры HDD 0;

¦ Int 46h — параметры HDD 1;

¦ Int 43h — знакогенератор EGA.

Сетевые адаптеры

Интерфейсы локальных сетей в ПК обеспечивают сетевые адаптеры, или сетевые интерфейсные карты (Network Interface Card, NIC). Адаптеры имеют передающую и принимающую части, которые в случае поддержки полного дуплекса должны быть независимы друг от друга. Задача передающей части: по получении со стороны центрального процессора (ЦП) блока данных и адреса назначения для передачи получить доступ к среде передачи, сформировать и передать кадр (добавить преамбулу, CRC-код), делая повторные попытки в случае обнаружения коллизий. Адаптер должен сообщить процессору об успехе или невозможности передачи. Приемная часть, просматривая заголовки всех кадров, проходящих в линии, «выуживает» из этого потока кадры, адресованные данному узлу уникальным, широковещательным или групповым способом. Адаптер можно программно настроить и на «неразборчивый» режим (promiscuous mode), в котором он будет принимать все кадры без разбора. Кадры принимаются в буфер и проверяются на отсутствие ошибок (длина кадра, корректность CRC). О приеме корректных кадров уведомляется центральный процессор и организуется передача кадра из локального буфера адаптера в системную память компьютера. Ошибочные кадры, как правило,

10.2. Сетевые адаптеры____________________________ =_______________________________ 411

игнорируются, хотя адаптер может собирать статистику их появления. На практике попадаются и адаптеры, не обнаруживающие ошибок в поврежденных кадрах. Диагностика сети с таким адаптером непроста.

Сетевые адаптеры для PC выпускаются для шин ISA, EISA, MCA, VLB, PCI, PC Card. Существуют адаптеры, подключаемые к стандартному LPT-порту PC; их преимущество — отсутствие потребностей в системных ресурсах (порты, прерывания и т. п.) и легкость подключения (без вскрытия компьютеров), недостаток — при обмене они значительно загружают процессор и не обеспечивают высокой скорости передачи («потолок» — 10 Мбит/с). Есть адаптеры и для шины USB. Сетевые адаптеры интегрируются и в некоторые модели системных плат.

Эффективная скорость обмена данными по сети очень сильно зависит от архитектуры сетевых адаптеров и, при прочих равных условиях, от скорости .передачи данных между локальной памятью адаптера и системной памятью компьютера, а также от возможности параллельного выполнения нескольких операций. В качестве «средств доставки» используются каналы прямого доступа к памяти (DMA), программный ввод-вывод (РЮ), прямое управление шиной. Стандартные 8-битные каналы прямого доступа шины ISA способны развивать скорость до 2 Мбайт/с, 16-битные — до 4 Мбайт/с. Кадр максимальной длины (1514 байт) они передают примерно за 1,3 или 2,6 мс соответственно. По сравнению с 12 мс, требуемыми для передачи кадра в среде Ethernet, это время относительно невелико. Однако для Fast Ethernet, где тот же кадр в среде передается за 1,2 мс, такая транспортировка оказывается слишком медленной. Более высокую скорость обмена с буфером адаптера обеспечивает режим программного ввода-вывода (РЮ), но он полностью загружает центральный процессор на время передачи. Более эффективны интеллектуальные адаптеры с прямым управлением шиной (bus mastering) ISA/ EISA, сочетающие относительно высокую скорость (до 8 Мбайт/с ISA 16 бит и до 33 Мбайт/с EISA). Однако для скорости 100 Мбит/с производительности шины ISA уже недостаточно. На сегодняшний день широко применяются адаптеры шины PCI, где для 32-разрядного интерфейса при частоте 33 МГц пропускная способность достигает 132 Мбайт/с. Но для технологии Gigabit Ethernet и этого только-только хватает, правда, у PCI есть резервы: переход на частоту 66 МГц и разрядность 64 бит, что позволяют далеко не все системные платы. Особенно эффективны активные адаптеры, имеющие собственный процессор, для шины PCI. Они выполняют передачи на полной скорости PCI, практически не загружая центральный процессор. Это свойство особенно важно для серверов. Параллельное выполнение операций подразумевает поддержку полного дуплекса — полную независимость принимающей и передающей частей, а также возможность одновременного выполнения приема кадра в буфер, передачи другого кадра и обмена данными между буферной памятью адаптера и системной памятью компьютера.

На производительность адаптера для ISA/EISA влияет и объем буферной памяти: при ограниченной (по сравнению со скоростью в линии) пропускной способности шины применяют буферную память объемом до 64 Кбайт, которую делят между передатчиком и приемником либо поровну, либо с преимуществом для передатчика. Для шины PCI при эффективных средствах доставки (интеллектуальное прямое управление шиной) для скорости 100 Мбит/с большой буфер не нужен —

412______________________________ Глава 10. Интерфейсы компьютерных сетей

достаточно по 2 Кбайт на приемник и передатчик. Однако адаптеры Gigabit Ethernet опять снабжают буфером значительного размера (256 Кбайт).

Адаптеры можно разделить на две группы — адаптеры для рабочих станций и адаптеры для серверов. Деление условно — адаптеры для рабочих станций могут иметь черты, относящиеся к серверным. Использовать простые карты в серверах не стоит — они могут стать узким местом сети и «пожирателями» ресурсов ЦП.

Адаптеры для рабочих станций проще и дешевле — для них не требуется (пока?) скорости выше 100 Мбит/с, полный дуплекс встречается редко, к использованию процессорного времени особо жестких требований не предъявляют. Долгие годы широко применяются адаптеры, программно совместимые с картами NE2000 — 16-битными неинтеллектуальными картами для шины ISA разработки Novell-Eagle. Совместимость с этой моделью имеют и ряд карт для шины PCI. Наиболее удобны и популярны двухскоростные карты 10/100 Мбит/с — для их подключения в современных сетях легко найти оптимальное место. Карты обычно имеют колодку для установки Boot ROM, современные модели часто обеспечивают возможность «пробуждения» по сети (remote wake up), поддерживают интерфейс DMI и ACPI. Для этого они имеют специальный дополнительный 3-проводный интерфейс — кабель с коннектором, подключаемый к системной плате. По этому кабелю системная плата с питанием в стандарте АТХ подает дежурное напряжение (линия +5VSB), даже когда основное питание на системную плату и все устройства не подается.

От этой линии питается «дежурная» принимающая схема, которая настроена на прием кадра специфического формата (Magic Packet) no сетевому интерфейсу. По приему этого кадра сетевой адаптер через кабель подает пробуждающий сигнал РМЕ на системную плату, которая дает сигнал на включение блока питания; компьютер включается и загружается ОС с поддержкой DMI. Теперь администратор может выполнить все запланированные действия, а по окончании ОС на компьютере, завершая свою работу, выключает питание.

Адаптеры для серверов должны иметь высокопроизводительную шину — сейчас используют PCI32/64 бит 33/66 МГц, раньше в серверах часто применяли шину EISA или МСА. Для серверных карт критична загрузка ЦП при обмене данными, поэтому эти карты наделяют интеллектом для прямого управления шиной и параллельной работы узлов адаптера. Полнодуплексные адаптеры должны поддерживать управление потоком по 802.3х. Ряд совершенных моделей поддерживают приоритизацию трафика по 802.1р, фильтрацию многоадресного трафика, поддержку ВЛС с маркированными кадрами (tagged VLAN), Fast IP, аппаратный подсчет контрольных сумм IP-пакетов. Поддержка ВЛС позволяет серверу, подключенному одной линией к коммутатору, быть членом нескольких ВЛС, определенных на всей локальной сети. Для повышения надежности серверные карты могут поддерживать резервирование линий (Resilient Link) — резервный адаптер и линия связи заменяют основной канал в случае его отказа. При этом резервному адаптеру присваивается МАС-адрес основного, чтобы сеть «не заметила» подмены. Резервирование линий должно поддерживаться программными драйверами, чтобы замена происходила прозрачно и для серверных приложений. «Самоизлечивающиеся» драйверы (Self-Healing Drivers) в случае обнаружения проблем функ-

10.2. Сетевые адаптеры______________________________________________ 413

ционирования («зависании») могут автоматически выполнить сброс и повторную инициализацию адаптера. Удаленная загрузка и пробуждение по сети серверам, как правило, не требуется.

Адаптеры (совместно с драйверами) могут поддерживать SNMP и RMON. Для серверов выпускаются и многопортовые (как правило, на 4 порта) адаптеры, конфигурируемые как для раздельного независимого использования, так и для резервирования друг друга. Такие карты позволяют экономить слоты PCI (для шины EISA проблема экономии слотов не была острой). Типовая скорость для серверных карт на сегодняшний день — 100 Мбит/с, производительность Gigabit Ethernet может быть востребована лишь очень мощными серверами.

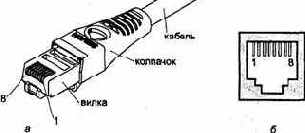

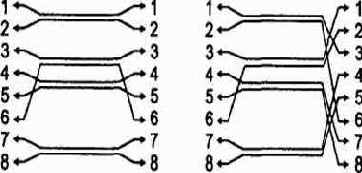

Адаптер может иметь один или несколько интерфейсных разъемов:

¦ BNC — коаксиальный разъем для подключения к сегменту сети 10Base2;

¦ AUI — розетка DB-15 для подключения внешних адаптеров (трансиверов)

lOBaseS, 10Base2, lOBaseT, lOBaseF, FOIRL;

¦ RJ-45 — 8-контактное гнездо для подключения кабелем «витая пара» к концентратору (хабу или коммутатору) lOBaseT, 100BaseTX и/или 100BaseT4;

¦ SC (пара), иногда ST — оптические разъемы для подключения к концентраторам 100BaseFX, lOOOBaseSX, lOOOBaseLX.

Для 10-мегабитных адаптеров характерны сочетания BNC+AUI или RJ-45+AUI, наиболее универсальные «Combo» имеют полный 10-мегабитный набор BNC/AUI/ RJ 45. Первые модели карт на 10 и 100 Мбит/с имели пару разъемов RJ-45 — каждый для своей скорости. При наличии нескольких разных разъемов (например, BNC и RJ-45) одновременно они не используются — адаптер не может работать в качестве повторителя. Большинство современных адаптеров имеют один разъем RJ-45 и поддерживают два стандарта — lOBaseT и 100BaseTX. Многопортовые серверные карты имеют несколько независимых адаптеров, каждый со своим интерфейсом.

Интерфейсные карты потребляют системные ресурсы компьютера.

¦ Пространство ввода-вывода — как правило, 4-32 смежных адреса из области, адресуемой 10-битным (для шины ISA) или 16-битным (EISA, PCI) адресом.

Используется для обращения к регистрам адаптера при инициализации, теку

щем управлении, опросе состояния и передаче данных.

¦ Запрос прерывания — одна линия (IRQ3,5,7,9,10,11,12 или 15), возбуждаемая по приему кадра, адресованного данному узлу, а также по окончании передачи кадра (успешной или безуспешной из-за коллизий). Без прерываний сетевые карты работать не могут, при некорректном назначении обращения к сети «зависают».

¦ Канал прямого доступа к памяти (DMA) используется в некоторых картах

ISA/EISA; для прямого управления (bus mastering) шины ISA пригодны только 16-битные каналы 5-7.

¦ Разделяемая память (adapter RAM) адаптера — буфер для передаваемых и принимаемых кадров — для карт ISA обычно приписывается к области верхней памяти (UMA), лежащей в диапазоне AOOOOh-FFFFFh. Карты PCI могут располагаться в любом месте адресного пространства, не занятого оперативной памятью компьютера. Разделяемую память используют не все модели карт.

414______________________________ Глава 10. Интерфейсы компьютерных сетей

¦ Постоянная память (adapter ROM) — область адресов для модулей расшире

ния ROM BIOS, 4/8/16/32 Кбайт в диапазоне COOOO-DFFFFh. Используется для установки ПЗУ удаленной загрузки (Boot ROM) и антивирусной защиты.

Под конфигурированием адаптера подразумевается настройка на использование системных ресурсов PC и выбор среды передачи. Конфигурирование, в зависимости от модели карты, может осуществляться разными способами.

¦ С помощью переключателей (джамперов), установленных на карте. Использу

ется на адаптерах первых поколений шины ISA. Для выбора каждого ресурса, а также среды передачи имеется свой блок джамперов.

¦ С помощью энергонезависимой памяти конфигурации (NVRAM, EEPROM),

установленной на карте с шиной ISA. Эти карты не имеют джамперов (jumperless),

но конфигурируются вручную. Для конфигурирования требуется специальная

утилита, специфическая для конкретной модели (семейства) карт.

¦ С помощью энергонезависимой памяти конфигурации, установленной на карте с

шиной EISA или МСА, и системной памяти конфигурирования устройств (ESCD для EISA). Конфигурирование ресурсов осуществляется пользователем с помощью системной утилиты ECU (EISA Configuration Utility) для шины EISA.

¦ Автоматическое — PnP для шин ISA и PCI. Распределение ресурсов осуществляется на этапе загрузки ОС.

Выбор среды и скорости передачи может быть ручным (программным) или автоматическим. В ряде случаев имеет смысл делать явные назначения, чтобы избегать сюPnPизов излишней автоматизации. Эти сюPnPизы, как правило, порождаются недостаточной согласованностью адаптеров и их драйверов. При этом драйвер не может правильно распознать установленный режим и воспользоваться его преимуществами. Автоматическая настройка вносит дополнительные задержки в процесс инициализации (при загрузке) и не со всяким сетевым оборудованием работает корректно. Для некоторых моделей карт с интерфейсом 10Base2 (BNC-разъем) предлагается расширенный режим, увеличивающий дальность связи до 305 м против штатных 185. При необходимости длинных сегментов этим режимом можно воспользоваться, но при условии, что он имеется и включен во всех картах данного сегмента. В утилитах конфигурирования могут предлагаться и дополнительные настройки — оптимизация для клиента или сервера, поддержка модема и некоторые другие. Их установка должна соответствовать конкретному применению.

Шина ACCESSBus

Последовательная шина ACCESS.Bus (Accessory Bus) разрабатывалась фирмой DEC как унифицированный недорогой интерфейс взаимодействия компьютера с внешними устройствами — клавиатурой, координатными устройствами, текстовыми устройствами (принтеры, считыватели штрих-кодов), мониторами (в плане обмена управляющей и конфигурационной информацией по каналу VESA DDC). История ACCESS.Bus начинается с 1991 г.; несколько позже в шину вели дополнительную спецификацию для взаимодействия с внутренними устройствами, например, интеллектуальными источниками питания (Smart Battery) и т. п. К внутренним относятся устройства системного управления SM (System Management), и в спецификации имеются точки соприкосновения с шиной SMBus, основанной на том же интерфейсе PC. Формально шина позволяет обмениваться сообщениями устройствам числом до 125 (предел принятой системы адресации). Над аппаратным протоколом PC в шине ACCESS.Bus имеется базовый программный протокол, с которым взаимодействуют протоколы конкретных подключенных устройств. Протоколы обеспечивают подключение/отключение устройств без перезагрузки ОС и автоматическое динамическое назначение адресов. Последняя доступная версия ACCESS.bus Specifications Version 3.0 опубликована ACCESS.bus Industry Group в 1995 г., дальнейшее описание сделано на ее основе.

На аппаратном уровне шина логически полностью соответствует шине PC со стандартной скоростью (до 100 Кбит/с) и 7-битной адресацией ведомых устройств. Здесь работают те же механизмы синхронизации и арбитража. Однако из всех возможных способов передачи и приема данных в ACCESS.bus основным является передача данных ведущим устройством и их прием ведомым устройством — это

428__________ Глава 11. Вспомогательные последовательные интерфейсы и шины

самый простой способ, при котором в каждой транзакции отсутствует смена направления передачи. Из этого следует, что для двустороннего обмена информацией все устройства должны поддерживать функции ведущего устройства (передатчика) и ведомого устройства (приемника).

Для совместимости с SMBus разрешена возможность чтения данных ведущим устройством и комбинированные передачи через условие 5г.

По электрическим сигналам имеются две спецификации, для внешних и внутренних устройств соответственно.

Спецификация для внешних устройств (Off-board ACCESS.bus), являющаяся основной для этой шины, определяет использование 4-контактного экранированного модульного разъема (MOLEX SEMCONN или AMP SDL), назначение контактов которого приведено в табл. 11.2. Хост-компьютер должен обеспечивать питание 5 В с током 50-1000 мА. Каждое устройство (и кабель), характеризуется потребляемым током I (мА) и вносимой емкостью сигнальных проводов С (пФ). Предельное число подключаемых устройств ограничивается суммарной вносимой емкостью (не более 1000 пФ) и током потребления. До ограничения по адресации (125 устройств) дело практически не доходит. Максимальная суммарная длина кабеля (без повторителей) не должна превышать 10 м. По сравнению с PC в шине ток нагрузки линий SDA и SCL увеличен до б мА (выходной ток низкого уровня). Для улучшения формы импульсов и защиты от статического электричества устройства рекомендуется подключаться к линиям SDA и SCL через последовательные резисторы 51 Ом. Входы микросхем рекомендуется защищать диодами, соединенными с шинами GND и +5 В.

Таблица 11.2. Назначение контактов внешнего разъема ACCESS.bus

Контакт Назначение Цвет провода

1

2 SDA Зеленый

3 +5 В (питание устройств) Красный

4 SCL Белый

Таблица 11.3. Разъем ACCESS.Bus (VESA)

|

Контакт |

Назначение |

|

1 |

GND |

|

2 |

Ключ |

|

3 |

SDA |

|

4 |

+5 В (питание устройств) |

|

5 |

SCL |

11.1. Последовательные шины на базе I2C_______________________________ 429

Спецификация для внутренних устройств (On-board ACCESS.bus) рассчитана на меньшие токи нагрузки (350 мкА); здесь допускаются последовательные резисторы большего сопротивления. Вместо ограничения на вносимую емкость задаются требования к фронтам и спадам сигналов. Эта спецификация была введена только в 1995 г., она нацелена на совместимость с устройствами SMBus, и в нее введены дополнительные ограничения на максимальные длительности различных фаз, соответствующие SMBus.

Базовый протокол шины ACCESS.bus 3.0 состоит из двух наборов: протокол РА для устройств с программируемым адресом (Programmable Address) и протокол FA для устройств с фиксированным адресом. В устройстве (как внешнем, так и внутреннем) может быть реализован любой из них или оба. Предыдущая версия спецификации описывала только внешние устройства РА; внутренние устройства с FA называются SM-устройствами (System Management). Протокол FA практически соответствует шине SMBus, описанной ниже, без «архитектурных излишеств» в виде РЕС и динамического назначения адресов. Устройства SM могут общаться с хостом по протоколу Write Word (см. ниже). Базовый протокол РА основан на передаче однонаправленных сообщений (см. ниже). Шина ACCESS.bus является хост-центрической: сообщения передаются от устройства к хосту и от хоста к устройству; исключением является попытка сброса устройства-двойника (см.

ниже). После включения питания устройства должны отвечать только на «дежурный» адрес 0110 111; в процессе конфигурирования каждому устройству назначается личный адрес. В рабочем состоянии шина позволяет обнаруживать подключение новых устройств и их конфигурировать без перезагрузки («горячее подключение»).

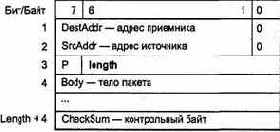

Сообщения передаются в виде пакетов, формат пакета приведен на рис. 11.3. Адрес назначения DestAddr воспринимается получателем аппаратно (это адрес ведомого устройства PC). Адрес источника SrcAddr позволяет получателю идентифицировать источник данных (и определить, куда посылать ответ). Флаг протокола Р позволяет различать назначение тела пакета: Р=0 — «полезные» данные устройства (Device Data Stream); P=l — управление/состояние (control/status). Поле Length определяет длину тела пакета (в байтах); само тело (Body) размещается в последующих байтах. Контрольный байт Checksum является результатом выполнения функции XOR (Исключающее ИЛИ) над всеми предшествующими байтами пакета начиная с адреса приемника. Признаком целостности пакета является нулевой результат функции XOR от всех байтов пакета включая контрольный. Подлежат отработке только пакеты с корректным контрольным байтом. Минимальная длина всего пакета — 4, максимальная — формально 131 (127 байт тело и 4 байта обрамления). Однако максимальную длину пакета ограничивает и время, разрешенное устройству для передачи пакета.

Каждому устройству назначается свой адрес, на который оно должно отзываться битами подтверждения при приеме сообщения. Адрес выражают однобайтным числом, причем всегда четным, поскольку в PC 7-битный адрес дополняется младшим битом RW, нулевым в ACCESS.bus. Адрес 50h всегда назначается хост-компьютеру, адрес 10h зарезервирован для хоста SM-устройств. Адрес 6Eh является

430

Глава 11. Вспомогательные последовательные интерфейсы и шины

«дежурным» адресом, на который отзываются лишь устройства с неназначенным личным адресом. Для личных адресов устройств остаются диапазоны 02-4ЕН; 52-GCh; 70-FEh — 125 адресов с некоторыми исключениями, зарезервированными для фиксированных адресов SM-устройств и мониторов.

Рис. 11.3. Формат пакета сообщения ACCESS.Bus

Для ACCESS.bus определено 9 протокольных сообщений (у них флаг Р=1), обяза тельных для реализации интерфейсных функций шины (автоконфигурирования). «Полезными» прикладными сообщениями могут обмениваться только сконфигурированные устройства и только после явного разрешения этого обмена.

Ниже перечислены сообщения от хоста к устройствам.

¦ Reset — сброс устройства и перевод его в режим ответа на «дежурный» адрес. Тело состоит из однобайтного кода FOh. Это же сообщение может послать и устройство, обнаружившее на шине помеху в виде устройства-двойника с тем же адресом. Послав это сообщение по своему же собственному адресу, устройство заставит двойника перейти на «дежурный» адрес.

¦ Identification Request — запрос идентификационной строки. Тело состо

ит из однобайтного кода Flh.

¦ Assign Address — назначение устройству, имеющему совпадающую идентификационную строку, нового адреса. Тело (длина 30) начинается с кода F2h, за которым следует 28-байтный идентификатор устройства, а за ним — байт нового адреса.

¦ Capabilities Request — запрос фрагмента информации о возможностях

устройства. В теле за кодом F3h следует 16-битный параметр — смещение

требуемых данных относительно начала структуры данных возможностей. Для

упрощения логики устройств параметр ограничивается значениями, обес

печивающими чтение первого фрагмента (с нулевым смещением), следующе

го и переспрос последнего переданного.

¦ Enable Application Report — разрешение передачи прикладных данных.

За кодом F5h следует байт кода операции: ООН — запрет, 01

¦ Presence Check — проверка наличия устройства по данному адресу. За кодом F7h следует нулевой байт (зарезервирован на будущее).

11.1. Последовательные шины на базе !2С_______________________________ 431

Далее перечислены сообщения от устройств к хосту.

¦ Attenti on —запрос на конфигурирование (устройство включилось и завершило автоинициализацию). Тело состоит из однобайтного кода EOh.

¦ Identification Reply — ответ на запрос идентификационной строки. Тело

(длина 29) содержит код Elh, за которым следует 28-байтная строка иденти

фикации.

¦ Capabilities Reply — ответ на запрос фрагмента описания возможностей.

Тело (длина 3-35) начинается с кода E3h, за которым следует 16-битное смещение (см. запрос) и собственно данные (0-32 байт). Хост собирает фрагменты, используя смещение.

Также в спецификации определены дополнительные протокольные сообщения, используемые для управления потреблением, распределением ресурсов и иных целей (у этих сообщений также флаг Р-1).

¦ Resource Requeset — запрос ресурса (от устройства к хосту). За кодом E5h

следует байт-описатель ресурса и необходимые данные. Команда позволяет

запросить адрес в личное пользование и освободить его; запросить сообщение

о текущем времени; запросить хост о сохранении блока данных, а также о воз

вращении его ббратно; запросить хост о сохранении питания на шине (для

окончания внутренних операций); запросить дополнительную полосу шины.

¦ Resource Grant — выделение ресурса, ответ хоста на запрос. За кодом F4h

следует описатель ресурса и необходимые данные.

¦ Application Hardware Signal—запрос устройства на генерацию высокопри

оритетного аппаратного сигнала хост-компьютеру. За кодом AOh следует байт со следующим кодом сигнала:

• 1 — Reset — попытка аппаратного сброса компьютера;

• 2 — Halt — вызов отладчика;

• 3 — Attention — генерация сигнала внимания (аппаратное прерывание).

¦ Application Test — команда от хоста на выполнение устройством приклад

ного теста (код Blh).

¦ Application Test Reply — сообщение устройством о результатах выполне

ния теста. За кодом Alh следует код результата (0 — успешное выполнение, иначе — ошибка) и 0-30 байт дополнительных данных.

¦ Application Status Message — сообщение устройством об изменении сво

его состояния (в прикладном плане). За кодом A2h следует нулевой байт, за ним байт состояния и 2 байта специфических данных. Байт состояния:

• 00 — готово;

• 01 — не готово;

• 02 — изменились свойства;

• 03 — потеряно внутреннее состояние;

• 04 — потеряны прикладные данные (может, и от переполнения).

432__________ Глава 11. Вспомогательные последовательные интерфейсы и шины

¦ Device Power Management Command — команда управления потреблением устройства. За кодом F6 следует байт кода операции:

• 00 — режим Run;

• 01 — режим Standby;

• 02 — режим Suspend;

• 03 — режим Shutdown;

• 04 — совет отключить питание;

• 05 — рестарт;

• 06 — сообщить режим потребления.

Остальные коды протокольных сообщений задаются разработчиком в соответствии со спецификой устройств. Напомним, что прикладные данные передаются с флагом Р=0.

Строка идентификации устройства ACCESS.bus длиной 28 байт состоит из ряда символьных полей — байта ревизии протокола (protocol revision), 7-байтного поля ревизии модуля (module revision), 8-байтных имен производителя (vendor name) и модуля (module name), за которым следует 32-битный уникальный номер устройства (device number). Этот номер может быть либо фиксированным (уникальность обеспечивает производитель, что недешево), либо случайным числом, генерируемым по включению (на весь сеанс работы).

Системное ПО, распознавая устройство для подключения драйверов, не должно руководствоваться этой строкой — возможности устройства (Capabilities) описываются (и сообщаются) в специальной структуре данных. Эта структура зависит от типа устройства.

На уникальности идентификатора и основан механизм автоконфигурирования: на запрос идентификатора по «дежурному» адресу отвечают все устройства, еще не имеющие личных адресов. Однако в ходе арбитража до конца сообщения доходит только одно из этих устройств, после чего хост ему назначает личный адрес. В следующем общем опросе идентификаторов «победит» уже другое устройство и так далее, пока всем устройствам не будут назначены личные адреса (об этом хост узнает по отсутствию ответа на общий опрос). Устройство-«новичок» на шине заявит о своем появлении сообщением Attenti on, в ответ на которое хост выполнит вышеописанную процедуру идентификации и назначения адреса.

Спецификация ACCESS.bus определяет структуру программного обеспечения на хост-компьютере. Центральным элементом ПО является менеджер шины — ACCESS.bus Manager — программный драйвер, управляющий всеми операциями с устройствами, подключенными к шине. Этот драйвер, с одной стороны, связывается с аппаратными средствами хост-контроллера через драйвер минипорта MPD; с другой стороны, к нему обращаются драйверы устройств. Прикладное ПО обращается либо к драйверам нужных устройств, либо к менеджеру шины (но никак не напрямую к хост-контроллеру). Менеджер шины инициализирует шину и управляет ею, определяя вновь подключенные и отключенные устройства. Он связывает драйверы устройств (или прикладное ПО) с самими устройствами, проверяет входящие сообщения и работает как двунаправленный коммутатор данных,

11.1. Последовательные шины на базе I2C_______________________________ 433

переформатирующий и буферирующий входящие и исходящие сообщения. Драйвер мини-порта MPD (Mini Port Driver) служит для изоляции менеджера шины от аппаратных особенностей хост-контроллера. Драйверы устройств являются двусторонними интерфейсами между прикладными программами и специфическими устройствами.В спецификации ACCESS.bus описываются программные интерфейсы драйверов (Device Driver, Mini Port Driver), а также протоколы для клавиатур, указателей (Locator), мониторов, батарей и текстовых устройств.

Шина I

Шина Inter 1C Bus (шина соединения микросхем), или, кратко, PC, — синхронная последовательная шина, обеспечивающая двустороннюю передачу данных между подключенными устройствами. Шина ориентирована на 8-битные передачи. Передача данных может быть как одноадресной, к выбранному устройству, так и широковещательной. Уровни сигналов — стандартные, совместимые с широко распространенной логикой ТТЛ, КМОП, N-МОП, как с традиционным питанием +5 В, так и с низковольтным (3,3 В и ниже). Микросхемы с интерфейсом PC, как правило, имеют аппаратную поддержку протокольных функций. Протокол позволяет взаимодействовать на одной шине устройствам с различным быстродействием интерфейса. Требования к временным параметрам сигналов весьма свободные, так что на компьютерах и микроконтроллерах, не имеющих аппаратной поддержки шины PC, ее протокол может быть реализован даже чисто программно.

Шина PC используется уже давно, ее официальная версия 1.0 вышла в 1992 г. По сравнению с предшествующими (черновыми) версиями, здесь отсутствует (как запутанная и неиспользуемая) возможность программного задания адреса ведомого устройства. Также отсутствует низкоскоростной режим (Low speed), являющийся частным случаем стандартного режима — Standard Mode (5) — со скоростью 0-100 Кбит/с. В версии 1.0 появились определение быстрого режима — Fast Mode (F) — со скоростью 0-400 Кбит/с и связанные с ним изменения требований к форме сигнала и фильтрации помех. Также здесь веден режим 10-битной адресации устройств. Версия 2.0 вышла в 1998 г., когда интерфейс PC стал фактиче-

422 Глава 11. Вспомогательные последовательные интерфейсы и шины

В версии 2.1 (2000 г.) уточнены некоторые моменты, касающиеся временных диаграмм в режиме Hs. Приведенная здесь информация основана на спецификации шины PC версии 2.1, доступной на сайте www.philips.com. Параметры интерфейсных сигналов приводятся в п. 11.1.4, где они сопоставляются с требованиями SMBus и ACCESS.Bus.

Интерфейс PC использует две сигнальные линии: данных SDA (Serial Data) и синхронизации SCL (Serial Clock). В обменах участвуют два устройства — ведущее (master) и ведомое (slave). Ведущее и ведомое устройства могут выступать в роли и передатчика, и приемника данных. Протокол допускает наличие на шине нескольких ведущих устройств и имеет простой механизм арбитража (разрешения коллизий).

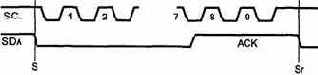

Протокол обмена для обычных устройств F/S иллюстрирует рис. 11.1. Обе сигнальные линии имеют нагрузочные резисторы, «подтягивающие» их уровень к напряжению питания. На устройстве к каждой линии подключен приемник и передатчик типа «открытый коллектор» («открытый сток»), у ведомого устройства передатчик на линии SCL не обязателен. Все одноименные передатчики соединяются по схеме «Монтажное И»: уровень в линии будет высоким, если все передатчики пассивны, и низким, если хоть у одного передатчика выходной транзистор открыт. В покое (Idle, исходное состояние шины) все передатчики пассивны. Синхронизацию задает ведущее устройство, но ведомое, если оно не имеет достаточного быстродействия, может замедлять обмен данными.

Рис. 11.1. Протокол передачи данных I2C

Начало любой передачи — условие Start — инициируется ведущим устройством, убедившимся в том, что шина свободна (высокий уровень сигналов SCL и SDA). Условие Start (на диаграммах обозначается как S)— перевод сигнала SDA из высокого в низкий при высоком уровне SCL Завершается операция переводом сигнала SDA из низкого уровня в высокий при высоком уровне SCL — условие Stop (обозначается как Р), также вводящееся ведущим устройством. При передаче данных состояние линии SDA может изменяться только при низком уровне SCL, биты данных считаются действительными во время высокого уровня SCL Ведущее устройство может начать очередную передачу вслед за текущей, не вводя условие

11.1. Последовательные шины на базе I2C_______________________________ 423

Stop, — это называется repeated Start (повторный старт, обозначающийся S г). В протоколе условия S и Sr почти равнозначны. Каждая посылка данных состоит из 8 бит данных, формируемых передатчиком (старший бит — MSB — передается первым), после чего передатчик на один такт освобождает линию данных для получения подтверждения. Приемник во время девятого такта формирует бит подтверждения Ac k, по которому передатчик убеждается, что его «услышали». После передачи бита подтверждения ведомое устройство может задержать следующую посылку, удерживая линию SCL на низком уровне. Ведомое устройство в режимах F/S может замедлить передачу по шине и на уровне приема каждого бита, удерживая SCL на низком уровне после его спада, сформированного передатчиком. Поэтому ведущее устройство должно генерировать сигнал SCL не «вслепую», а анализируя состояние линии SCL: сняв этот сигнал, новый импульс (открытие ключа передатчика) оно имеет право вводить, лишь убедившись, что сигнал SCL вернулся в пассивное состояние (высокий уровень). В противном случае синхронизация будет потеряна. Сигнал SCL может быть растянут и другим устройством, пытающимся захватить шину в это же время. Тактовый сигнал SCL не обязательно будет равномерным: время его нахождения на низком уровне будет определяться максимальным временем, в котором его захочет удержать самое медленное из устройств, участвующих в данном обмене (даже и конфликтующих); время нахождение на высоком уровне будет определяться самым быстрым из конфликтующих ведущих устройств.

Коллизия (конфликт) на шине может возникнуть, когда два (или более) устройства, убедившись в покое шины, одновременно (или почти одновременно) инициируют обмен данными. Все они управляют линиями SCL и SDA и наблюдают за ними. Если устройство, передающее единицу (высокий уровень), в данном такте на линии SDA видит ноль (низкий уровень), оно должно признать свой проигрыш в конфликте и освободить линии SCL и SDA (при этом ему позволительно управлять линией SCL до конца передачи текущего байта).

Выигравшее устройство даже и не заметит проигравших конкурентов и продолжит работу. Арбитраж может закончиться в любом месте посылки, формируемой ведущим устройством. Искажения информации, передаваемой выигравшим устройством, не происходит (приятное отличие от коллизий в сетях Ethernet). Если ведущее устройство, проигравшее в конфликте, имеет и функции ведомого устройства, по признанию проигрыша оно должно перейти в режим ведомого, поскольку конфликт мог быть вызван и попыткой обращения к нему победившего ведущего устройства.

Бит подтверждения АС К, вводящийся в конце каждого байта устройством-приемником, выполняет несколько функций. Когда передатчиком является ведущее устройство, приемник (ведомый) должен вводить нулевой бит АС К, свидетельствующий о нормальном получении очередного байта. Единичный бит АС К (нет подтверждения) в ответ на посылку адреса свидетельствует об отсутствии адресованного ведомого устройства на шине или его занятости внутренними процессами. Отсутствие подтверждения байта данных свидетельствует о занятости устройства. Не получив бита подтверждения, ведущее устройство должно сформировать условие Stop, чтобы освободить шину. Когда ведущее устройство является приемником, оно должно формировать нулевой бит АС К после каждого принятого байта, кроме последнего. Единичный бит АСК в этом случае является указанием ведомому

424__________ Глава 11. Вспомогательные последовательные интерфейсы и шины

устройству на окончание передачи — оно теперь должно освободить линии SDA и SCL, чтобы ведущее устройство смогло сформировать условие Р или S r.

На вышеописанной физической основе строится протокол обмена данными по PC. Каждое ведомое устройство имеет свой адрес, уникальный на шине. В начале любой передачи ведущее устройство после условия S или S г посылает адрес ведомого устройства или специальный адрес (табл. 11.1). Ведомое устройство, опознавшее свой адрес после условия Start, становится выбранным; оно обязано ответить подтверждением на адрес и последующие сигналы со стороны ведущего устройства, до получения условия Р или 5г.

В первоначальном варианте интер фейса разрядность адреса устройства составляла 7 бит, впоследствии был введен и режим 10-битной адресации, совместимый с 7-битной. На одной шине могут присутствовать устройства и с 7-битной, и 10-битной адресацией.

При 7-битной адресации в первом байте после S (Sr) ведущее устройство передает 7 бит адреса (А[6:0] в битах [7:1]) и признак операции RW (в бите О RW=1 — чтение, RW=0 — запись). Адреса ведомых устройств не должны попадать в области, указанные в таблице. Диапазоны адресов устройств различных типов централизованно выдаются изготовителям микросхем фирмой Philips. Для микросхем памяти, например, 7-битный адрес содержит две части: старшие 4 бита А[б:3] несут информацию о типе устройства (EEPROM — 1010), а младшие 3 бита А[0:2] определяют номер устройства данного типа на шине. Микросхемы с интерфейсом PC имеют три адресных входа, коммутацией которых на логические уровни 1 и 0 задается номер устройства, на который оно «отзовется», а тип устройства «зашит» в нем самом его изготовителем.

Когда ведущее устройство является передатчиком данных, оно в первом байте передает адрес ведомого устройства, при этом RW=0. Выбранное ведомое устройство отзывается подтверждением (АСК=0), после чего ведущее устройство посылает один или несколько байт данных, на каждый из которых ведомое устройство должно отвечать подтверждением.

Когда ведущее устройство является приемником данных, оно в первом байте передает адрес ведомого устройства с RW=1. Выбранное ведомое устройство также отзывается подтверждением (АСКНЗ), после чего происходит смена направления передачи и данные уже передает ведомое устройство. Ведущее устройство подтверждает каждый принятый байт, кроме последнего.

Эти передачи могут завершаться условием Р, вводимым ведущим устройством, после которого шину может захватить любое ведущее устройство. Возможны и комбинированные передачи, когда ведущее устройство после окончания очередного обмена не отдает шину, а формирует повторный старт (Sr), после чего обращается к тому же или иному устройству.

Отметим, что спецификация PC не оговаривает правил модификации внутреннего (для микросхемы) адреса данных при последовательных обращениях — их определяет разработчик устройства в соответствии с его функциями. Для памяти естественен автоинкремент адреса, упрощающий последовательные обращения. Для регистроориентированных устройств автоинкремент обычно не нужен.

11.1. Последовательные шины на базе I2C

425

|

0000000 |

0 |

|

0000 000 |

1 |

|

0000 001 |

X |

|

0000 010 |

X |

|

0000 011 |

X |

|

0000 1ХХ |

X |

|

1111 1ХХ |

X |

|

1111 ОХХ |

X |