Настройка симулятора

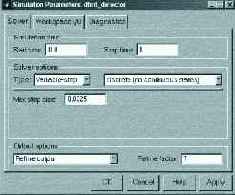

После того, как вся модель построена и скомпонована, можно запустить симуляцию и проследить на разных стадиях весь процесс детектирования цифры. Перед запуском симуляции модели необходимо задать параметры симуляции, к которым относятся время, способ и максимальный шаг симулятора, если выбран не фиксированный шаг. Пример диалогового окна настройки показан на рис. 10.

Проверка блока логики

Блок логики, как уже было сказано выше, обеспечивает временные характеристики приёмника и общую логику работы. В нём происходит подсчёт числа одинаковых определений номеров строки и столбца, сравнение этого количества с заданным временным порогом и выработка решения о том, что пришла новая цифра DTMF. Об этом сообщается на индикаторе, расположенном на верхнем уровне модели.

Проверка блоков расчёта периодов двух составляющих сигнала

Для этого следует подключить осциллограф к месту, где происходит вычисление периода. Результат представлен на рис. 16.

Проверка работы детектора наличия сигнала

Детектор наличия сигнала, принимающий решение о том, есть сигнал или нет, должен адаптироваться к интенсивности сигнала и шума. Чтобы проверить положение порога срабатывания, можно вывести уровень шума и интенсивности сигнала на осцилло-граф. Пример того, что может получиться, показан на рис. 14.

Проверка работы режекторных фильтров

Сначала нужно проверить работу сигнальной части модели — блоков генерации сигнала, измерения интенсивности сигнала и шума и режекции второй составляющей. Спектр сигнала на выходе генератора, посылающего цифру “1”, показан на рис. 11.

Проверка всей модели

После проверки всех блоков по отдельности и коррекции неточностей можно снова запустить модель и убеиться, что она работает. Теперь остаётся только проверить работу модели в граничных условиях, то есть при отклонениях частоты, амплитуды, наличия шумов и так далее, а так же самый важный тест — несрабатывание приёмника на речь.

Так как моделирование должно полностью повторять параметры моделируемой системы, необходимо добавить округление после каждой операции умножения и проверку на допустимые границы после каждой операции сложения. Блоки усиления сигнала и сумматоры имеют встроенную возможность входить в состояние “насыщения” при достижении определённого значения. Для этого в их параметрах необходимо активировать опцию “Saturate on integer overflow”. Для округления можно использовать блок из пакета Simulink, называемый “Rounding function”. В его параметрах следует указать, какую функцию округления использовать: округление (round), усечение (floor) или другую.

Как видно из вышеописанного, пакет

Как видно из вышеописанного, пакет Simulink позволяет реализовать довольно сложный алгоритм, разбить его на блоки и анализировать их как все вместе, так и по отдельности. Наглядность представления модели в Simulink позволяет легко менять структуру, “обвешивать” модель различными “датчиками” — осциллографами, спектроанализаторами и индикаторами. Процесс отладки становится красивым увлекательным занятием, результаты наглядны и однозначны. Для точного соответствия вычислений в Simulink и в ЦПОС, в модель вводятся элементы, обеспечивающие моделирование в арифметике с фиксированной запятой. Например, у результатов умножения можно отбрасывать дробную часть, а у сумматоров включить опцию “Integer overflow”, то есть режим переполнения 16-разрядного аккумулятора. Построенная с помощью Simulink, модель приёмника DTMF уверенно принимает тестовый сигнал, удовлетворяет требованиям ITU-T и может являться пособием для создания подобных устройств на ЦПОС и микроконтроллерах. Данная модель была создана сначала на языке MATLAB (m-file), для удобства настройки параметров по блокам была смоделирована в Simulink, после чего её перенесли на DSP. Она действительно работает на 16-разрядном процессоре, выполняя все спецификации ITU-T.

В заключение автор считает своим долгом поблагодарить руководителя проекта “MATLAB для DSP” проф. Ланнэ А.А. за постановку задачи и помощь в выполнении данной работы, фирму «SoftLine», предоставившую для этой работы лицензионую версию программы MATLAB v5.3, а также инженера «Лониис» Гусеву М.Н. за помощь в тестировании модели на 16-бит DSP фирмы «Analog Devices».

Литература

1. Анохин В.В., Ланнэ А.А. MATLAB для DSP. Моделирование аналого-цифрового преобразования. Часть 1 // Chip News. — 2000. — № 2. — С. 3–7.

2. Анохин В.В. MATLAB для DSP. Моделирование аналого-цифрового преобразования. Часть 2 // Chip News. — 2000. — № 3. — С. 26–29.

Заполнение блока “Logic sinth.”

Блок логики легче всего реализовать в виде S-функции — специальной конструкции языка MATLAB. Но для наглядности представим блок логики в графическом виде (рис. 9).

Заполнение блока “Notch filter”

Построим два одинаковых блока режекторных фильтров. Модель одного из них представлена на рис. 1.

Заполнение блока “Power estimator and signal detector”

Изначально алгоритм был предложен и объявлен в Internet для реализации на 8-бит процессорах, что накладывало серьёзные ограничения на операции умножения с накоплением, поэтому использовался сложный алгоритм адаптации уровня шума. Для реализации на 16-бит ЦПОС с 32-бит умножителем можно использовать более простые алгоритмы. В частности, вместо мощности сигнала можно вычислять интеграл от абсолютного значения сигнала. Соответствующий алгоритм реализован в виде схемы, изображённой на рис. 6.

Заполнение блоков “Row freq. detector” и “Column freq. detector”

Подсчёт частоты сигнала состоит из вычисления целой и дробной частей периода сигнала в интервалах дискретизации. Соответствующий модуль в Simulink может быть реализован так, как показано на рис. 5.